# WARSAW UNIVERSITY OF TECHNOLOGY

DISCIPLINE OF SCIENCE AUTOMATION, ELECTRONICS, ELECTRICAL ENGINEERING AND SPACE TECHNOLOGIES

FIELD OF SCIENCE ENGINEERING AND TECHNOLOGY

# Ph.D. THESIS

Rafał Kopacz, M.Sc.

Medium voltage power converters with SiC power devices

Supervisor

Jacek Rąbkowski, Ph.D., D.Sc.

**Auxiliary supervisor**

Michał Harasimczuk, Ph.D.

**WARSAW 2023**

### Acknowledgements

First and foremost, I would like to thank my supervisor and mentor in the world of power electronics, Prof. Jacek Rąbkowski. His passion for power electronics and working attitude guided me through my whole studies, always ready to support me on my course to Ph.D.

Furthermore, I would like to give my gratitude to all my colleagues from Prof. Rąbkowski's research group. Special thanks go to Grzegorz Wrona and former lab member Kamil Kozdrój, who gave me invaluable advice when I was making my first steps in experimental power electronics. I am also grateful to all fellow Ph.D. candidates with whom I shared office, lab space and had the pleasure of having countless discussions on power electronics and other subjects: Przemysław Trochimiuk, Krzysztof Kalinowski, Dawid Zięba and Dr. Piotr Majtczak. I would also like to thank current and former lab members and M.Sc. graduates: Dr. Mariusz Zdanowski, Dr. Rafał Miśkiewicz, Dr. Szymon Piasecki, Krzysztof Frąc, Hubert Skoneczny, and Bartosz Lasek. Last but definitely not least, I would like to thank my auxiliary supervisor, Dr. Michał Harasimczuk, whose bright ideas and support have greatly helped in the progress of my Ph.D.

My deep gratitude also goes to Prof. Johann Kolar and Prof. Dimosthenis Peftitsis, who invited me to temporarily join their research groups at ETH Zurich in Switzerland and NTNU in Norway, which gave me priceless experience working in top research groups in power electronics. Moreover, I would like to thank all the colleagues I have met and had the opportunity to work with during my stays abroad, especially Dr. Jonas Huber, Dr. David Menzi, Dr. Florian Krismer, Dr. Ole-Christian Spro, Dr. Andreas Giannakis, Dr. Gard Rodal.

Finally, I want to express my gratitude to people who are especially important in my life. My family, brothers Łukasz and Marek, Milena's family, and specifically my parents Aleksandra and Mirosław. I am deeply grateful to Milena for her love and support, which helped me extensively during my Ph.D. life.

Without all of you, this work would not have been possible; thank you very much.

Rafał Kopacz

Warsaw, September 2023

#### **Abstract**

Title: Medium voltage power converters with SiC power devices

The thesis presents considerations regarding power electronic systems based on Silicon Carbide power devices dedicated to applications in the medium voltage range. More specifically, the topics under consideration are modeling of medium voltage SiC power devices, focusing on the characterization method for the transistor output capacitance, used for accurate switching loss determination; a power loss estimation method for converters, established on a simple experimental setup; a comprehensive study, founded on experimental models, for various converter solutions dedicated for medium voltage power electronics with SiC power devices, including two-level, multilevel, series connection, and quasi-two-level methods; and novel approaches for dc-dc converters converging soft-switching techniques with the quasi-two-level method, aiming at improving the efficiency and power density. The dissertation consists of five core publications, which are preceded by an introduction briefly describing the subjects, the primary motivation for the specific concepts, an overview of the prior findings from the literature, as well as accentuating the contribution of the papers. Even though SiC power devices have been researched for several years, there are still limitations to the proper utilization of Silicon Carbide power devices for medium voltage applications, such as adequate semiconductor modeling, accurate power loss estimation, or the choice of a suitable topology. Thus, these issues are addressed within the thesis. All in all, it is shown that employing SiC-based power devices provides a myriad of opportunities for medium voltage power electronics applications, such as improved efficiency or higher power density, which surpasses the formerly-used Silicon-based power electronics.

**Keywords**: electric energy conversion, multilevel converters, power electronics, power converters, SiC MOSFET, series connection of power transistors.

#### Streszczenie

**Tytuł**: Przekształtniki energoelektroniczne średniego napięcia z przyrządami mocy z węglika krzemu

W rozprawie przedstawiono rozważania dotyczące układów energoelektronicznych dedykowanych do pracy w zakresie średnich napięć i wykonanych z wykorzystaniem półprzewodnikowych elementów mocy z węglika krzemu. Praca zawiera opis modelowania przyrządów mocy pracujących w przekształtnikach średniego napięcia z elementami z weglika krzemu, skupiając się na metodzie charakteryzacji pojemności wyjściowej tranzystora, wykorzystywanej do dokładnego określania strat łączeniowych; metodę estymacji strat mocy w elementach przekształtnika opartej o prosty układ eksperymentalny; studium porównawcze oparte o modele eksperymentalne dla różnych rozwiązań przekształtnikowych dedykowanych dla energoelektroniki średniego napięcia z uwzględnieniem wykorzystania tranzystorów mocy obejmujących układy dwupoziomowe, wielopoziomowe, a także oparte o szeregowe łączenie i metodę quasi-dwupoziomową; oraz nowatorskie rozwiązania przekształtników prądu stałego łaczące techniki miękkiego przełączania i sterowania quasi-dwupoziomowego, mające na celu poprawę jego sprawności i gęstości mocy. Rozprawa składa się z pięciu głównych publikacji, które poprzedzone są wstępem krótko opisującym tematykę, główną motywacją przedstawianych koncepcji, przeglądem dotychczasowych dokonań z literatury naukowej, a także zaakcentowanie kluczowych osiągnięć w artykułach. Mimo że elementy półprzewodnikowe z węglika krzemu są badane już od kilku lat, to nadal istnieją istotne ograniczenia, takie jak nieprecyzyjne modelowanie półprzewodników, niedokładne określanie strat mocy, czy wybór odpowiedniej topologii przekształtnika. Tym samym, kwestie te zostały poruszone w pracy. Podsumowując, wykazano, że zastosowanie przyrządów mocy z SiC w zastosowaniach energoelektroniki średniego napięcia umożliwia m.in.: poprawę sprawności i/lub uzyskanie wyższej gestości mocy, przewyższając parametry uzyskiwane przez układy zbudowane z elementów mocy wykonanych w technologii krzemowej.

**Słowa kluczowe**: energoelektronika, przekształtniki energoelektroniczne, przetwarzanie energii elektrycznej, SiC MOSFET, szeregowe łączenie tranzystorów mocy, przekształtniki wielopoziomowe

### **Abbreviations**

**BJT** bipolar junction transistor

**DFIG** double-fed induction generator

**EMI** electro-magnetic interference

**ESS** energy storage system

**FACTS** flexible AC transimission systems

FC flying capacitor

**GTO** gate turn-off

**IGBT** insulated gate bipolar transistor

**IGCT** integrated gate commutated thyristor

**JFET** junction field-effect transistor

LV low voltage

ML multilevel

MMC modular multilevel converter

**MOSFET** metal-oxide semiconductor field-effect transistor

MV medium voltage

**NPC** neutral point-clamped

**PMSG** permanent magnet synchronous generator

**PWM** pulse-width modulation

**RES** renewable energy sources

**SC** series connection

Si silicon

**SiC** silicon carbide

**SST** solid-state transformer

TCM triangular current mode

**THD** total harmonic distortion

**QSW** quasi-square wave

**WBG** wide band-gap

# **Contents**

| 1 | Introduction                      |                                                                          |                                                                    |    |  |  |

|---|-----------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|----|--|--|

|   | 1.1                               | Power                                                                    | electronic applications in medium voltage range                    | 11 |  |  |

|   | 1.2                               | Silicon                                                                  | n Carbide power devices advancing medium voltage power electronics | 17 |  |  |

|   | 1.3                               | Power                                                                    | converter topologies in medium voltage                             | 24 |  |  |

|   | 1.4                               | Motiv                                                                    | ation & aim                                                        | 30 |  |  |

|   | 1.5                               | Public                                                                   | ations included in the dissertation                                | 31 |  |  |

|   | 1.6                               | Other                                                                    | achievements                                                       | 32 |  |  |

| 2 | Contribution                      |                                                                          |                                                                    |    |  |  |

|   | 2.1                               | Model                                                                    | ling of medium voltage SiC power devices & converters              | 37 |  |  |

|   |                                   | 2.1.1                                                                    | From the measurement of COSS-VDS characteristic to the estima-     |    |  |  |

|   |                                   |                                                                          | tion of the channel current in medium voltage SiC MOSFET power     |    |  |  |

|   |                                   |                                                                          | modules [P1]                                                       | 37 |  |  |

|   |                                   | 2.1.2                                                                    | A Simple Method to Validate Power Loss in Medium Voltage SiC       |    |  |  |

|   |                                   |                                                                          | MOSFETs and Schottky Diodes Operating in a Three-Phase Inverter    |    |  |  |

|   |                                   |                                                                          | [P2]                                                               | 39 |  |  |

|   | 2.2                               | Topolo                                                                   | ogy concepts for MV power converters                               | 41 |  |  |

|   |                                   | 2.2.1                                                                    | Medium Voltage Power Switch in Silicon Carbide—A Comparative       |    |  |  |

|   |                                   |                                                                          | Study [P3]                                                         | 41 |  |  |

|   | 2.3 MV SiC-based dc-dc converters |                                                                          |                                                                    |    |  |  |

|   |                                   | 2.3.1                                                                    | Medium voltage flying capacitor dc-dc converter with high-freq-    |    |  |  |

|   |                                   |                                                                          | uency tcm-q2l control [P4]                                         | 43 |  |  |

|   |                                   | 2.3.2                                                                    | Investigation of soft-switching QSW technique in DC/DC SiC-based   |    |  |  |

|   |                                   |                                                                          | flying capacitor converter with Q2L control [P5]                   | 44 |  |  |

| 3 | Pub                               | lication                                                                 | S                                                                  | 47 |  |  |

|   | 3.1                               | From the measurement of COSS-VDS characteristic to the estimation of the |                                                                    |    |  |  |

|   |                                   | channe                                                                   | el current in medium voltage SiC MOSFET power modules [P1]         | 47 |  |  |

### CONTENTS

| 4 | Con | clusion                                                                  | 117  |

|---|-----|--------------------------------------------------------------------------|------|

|   |     | ing Capacitor Converter With Q2L Control [P5]                            | 105  |

|   | 3.5 | Investigation of Soft-Switching QSW Technique in DC/DC SiC-Based Fly-    |      |

|   |     | q2l control [P4]                                                         | 88   |

|   | 3.4 | Medium voltage flying capacitor dc-dc converter with high-frequency tcm- |      |

|   | 3.3 | Medium Voltage Power Switch in Silicon Carbide—A Comparative Study [P3   | ] 77 |

|   |     | and Schottky Diodes Operating in a Three-Phase Inverter [P2]             | 58   |

|   | 3.2 | A Simple Method to Validate Power Loss in Medium Voltage SiC MOSFETs     |      |

|   |     |                                                                          |      |

# Chapter 1

# Introduction

Medium voltage level has always been the most common choice for high-power power electronics applications, which is mainly associated with reduced current levels compared to low voltage systems. Smaller currents lead to significantly reduced conduction power losses, leading to better efficiencies, and also decreased volume and weight of the conductors cables or busbars. The interest in MV power electronics has been gaining even more traction lately, as the global aims for decarbonization of society and the industry are becoming more important every year. To reduce the CO<sub>2</sub> emission levels, the one target is the successful implementation of renewable energy sources, such as wind, solar, and hydropower plants, as the core generation sources since conventional energy sources, such as coal plants, are a source of extensive pollution, and do not correspond to the environment-friendly policies, such as Fit For 55, currently considered in the European Union. Taking into account the two most common RES - the wind and solar systems, the former has been mostly bound to MV levels since its inception, and the latter has also recently been introduced into a higher voltage range with PV strings rated at 1.5 kV and above. Moreover, the trend of reaching for higher and higher voltages every year is a recurring theme also for other systems, e.g., battery energy storages.

However, renewable energy sources are not the only applications for MV power electronic converters. A large variety of other applications employ such a voltage range. To name a few, e-mobility and electrical traction can be considered, as well as high-power motor drives, data centers, or smart grids. Considering the vast amount of power processed through these applications, energy conservation via more efficient means of energy conversion is also a focus to reduce the emission levels.

Therefore, there is a great need for efficient and reliable MV power electronics, preferably with limited volume and little effect on the surroundings, e.g., through electromagnetic or acoustic interference. The conventional approach to constructing medium voltage power

electronic converters is to use power semiconductor devices based on well-known Silicon technology, usually in the form of IGBTs, GTOs, or IGCTs. However, the advances in WBG semiconductor technology, and especially Silicon Carbide, have brought the well-performing MOSFET into the medium voltage range. While currently available devices are bound to up to 3.3 kV breakdown voltage, the prototypes of devices rated at 10 kV and above have already been presented. Even though higher voltages can already be reached with Si devices, SiC brings many other advantages compared to standard Si-based semiconductors. Namely, they are characterized by better switching capabilities, lower power losses, as well as higher sustainable temperatures, which provide the possibility to construct MV power converters with substantial power density and extremely high efficiencies. SiC-based power devices have already surpassed state-of-the-art Si-based counterparts in many ways, and it is predicted that they will even become more auspicious in the future.

While plenty of MV SiC-based power converters have already been presented both in academia and industry, there are still many issues to be resolved before the entirely appropriate employment of SiC semiconductors in MV power converters can be achieved. For example, since the rapid switching of SiC devices induces much more severe issues with parasitic components in the circuits, special care has to be given to the hardware design of the system. Moreover, the more complex structure of the SiC chips requires the introduction of new models and characterization methods. Furthermore, this can also be analyzed from a more general perspective: What topologies and control methods would result in the most efficient converters when SiC power devices are employed? Of course, this is just the tip of the iceberg, and the possible research opportunities seem nearly endless.

Thus, there is still a need to investigate SiC-based MV power electronic systems further so that full utilization of WBG power semiconductors can be achieved and sought-for, highly-efficient and compact MV power converters can be constructed.

The thesis outline is as follows. After a brief introduction showcasing the importance of MV power converters in today's society, a more thorough overview of power electronic applications is presented. It starts with the presentation of a plethora of MV systems that employ power converters. Then, the significance of the emerging Silicon Carbide semiconductor technology in MV is shown, especially considering the possible advancements over conventional Silicon-based power devices and the SiC-specific issues that are still to be resolved to utilize the technology fully. Further, the possible approaches to construct power converters employing SiC power devices are analyzed, focusing on different topologies. At last, the first part of the dissertation is finalized with the motivation behind the thesis and its aims.

In the second part of the dissertation, the contribution of the author within specific subtopics on MV SiC-based power converters is presented based on publications included in the thesis. The first area of interest is the modeling of medium voltage SiC power devices and converters, including the power loss estimation, where two papers are shown and briefly described. Further, the topic of topology concepts for MV power converters is considered and shown based on a publication considering several different approaches. In the next part, an exemplary MV dc-dc converter is exhibited, employing a novel topology and control scheme, utilizing the many advantages of SiC power semiconductor devices. This area is supported by two papers.

In the end, the thesis is concluded, showcasing that employing SiC-based power semiconductor devices helps to construct highly-performant MV power electronic systems, especially in terms of efficiency and power density, that easily surpass their Si counterparts.

## 1.1 Power electronic applications in medium voltage range

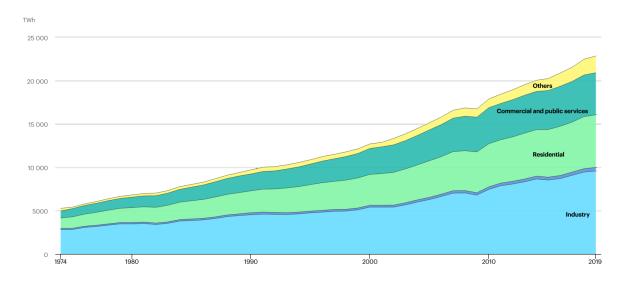

Global energy consumption is rising every year, with a rate of roughly 4% increase annually [1]. As can be seen in Fig. 1.1, a significant part of the share at 45% is due to industrial and transportation uses, which often employ MV systems.

At the same time, environmental concerns necessitate serious alterations in the global energy system, for example, through the shift of the energy sources from fossil fuel-based systems to RES or in the form of preserving the energy through more efficient conversion. While the current RES share in the global energy production is just slightly above 10%,

Figure 1.1: World electricity consumption by sector, 1974-2019 [1].

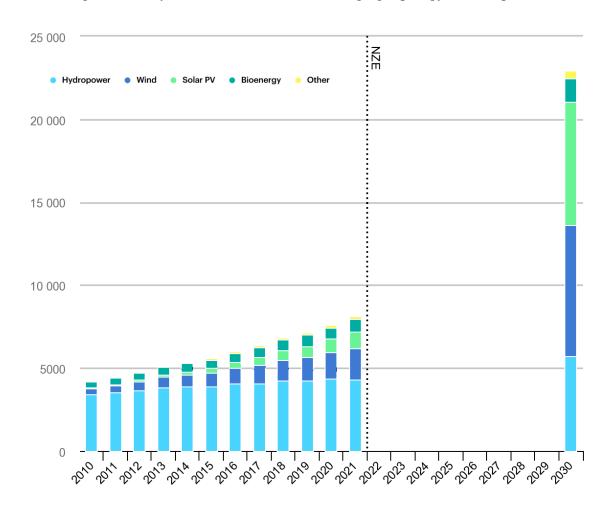

"global renewable capacity is expected to increase by almost 2 400 GW (almost 75%) between 2022 and 2027 in the IEA main-case forecast" (Fig. 1.2) [2]. Thus, the constantly increasing worldwide interest in RES requires more sophisticated power conversion systems, as well as a more decentralized approach to power systems, which also need to consist of distribution means based on power electronics, such as smart grids that usually favor MV instead of HV.

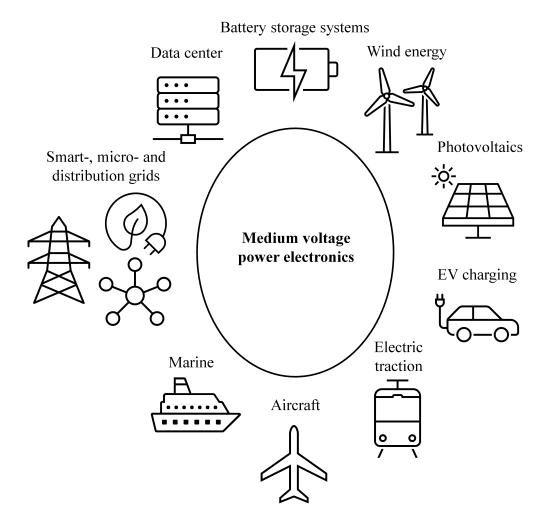

Furthermore, nowadays, almost every newly installed power system facilitates some kind of power electronics, either to increase their performance or to enable higher flexibility. Hence, there is a vast area for MV power converter applications, ranging from industry applications through e-mobility and transportation, RES, distribution and generation, and many, many more (see Fig. 1.3); which are addressed in the following in more detail.

Starting off, RES systems are considered an emerging topology for MV power electron-

Figure 1.2: Renewable power generation by technology in the Net Zero Scenario, 2010-2030 [2].

Figure 1.3: A vast application range for MV power electronics.

ics. Wind energy harvesting employs MV levels for the wind turbines almost exclusively because of the expedited power levels, ranging from several hundred kW up to single MW [3]. Nowadays, the most common solution is a full-scale converter paired with either DFIG or PMSG so that a frequency decoupling between the motor and the grid is ensured, along with an extra opportunity for THD improvement. The dominant converter topologies currently include multilevel approaches, usually in ac-dc-ac configuration [4].

Recently, PV systems are also under consideration for MV expansion. Taking into account substantial PV power plants, MV collector grids are often considered for multi-string connection and grid integration [5, 6]. In this case, large-power SST systems are of interest, aiming at efficiency and mains current quality. On the other hand, MV is also introduced into single PV strings, with voltages as high as 1.5 kV already established [7]. However, for this kind of application, dc-dc non-isolated converters capable of managing the high PV voltage fluctuation are being considered.

With the introduction of more and more RES into the electric power systems of the future, which can be quite unpredictable in regard to providing a reliable power supply, and moving further away from conventional, stable fossil-based power plants, the mismatch between the power demand and availability may become higher every year. Already today, there are often fluctuations ranging from too much generation (e.g., from PV systems that have to be shut down to not exceed the grid voltage) to insufficient power that could potentially lead to blackouts. Therefore, MV ESS has to be included in power systems of the future [8], while these are also already considered for other applications, for example traction grid support [9, 10] or to supply the energy for heavy-duty electric vehicles [11]. In general, ESS can be categorized into two groups: those that require high power capability in a short span of time, e.g., employing battery stacks or supercapacitors for either load leveling or peak shaving applications, and the less frequent solution of long-term energy storage by means of, for example, pumped-storage hydroelectric systems. Depending on the type of the ESS and the grid connection, both dc-dc and ac-dc systems are considered.

With the rapid increase of EVs on the global market, a requirement for fast and reliable charging stations arises. In order to have EVs fully replace conventional internal combustion engine-based vehicles, there is a need for ultra-fast charging stations, which are capable of charging the batteries to 90% of SOC in about 10-15 minutes [12]. To achieve such results, a power of several hundreds of kW per vehicle is required. Thus, since the whole charging station power range resides in MW, a direct connection to the MV grid is a common choice [13]. Therefore, grid MV converters are a necessity, often also with bidirectional capability supporting vehicle-to-grid operation or in an SST topology. Moreover, MV level is also considered for the DC distribution grids for EV charging stations [14], with the mentioned requirements for MV dc-dc converters as well.

Supplying the power to the rolling stock is also a domain of MV. The traction grid voltage levels and type can vary; 1.5 and 3 kV DC lines are used in certain countries such as Poland, Italy, or France, while AC systems with 15 and 25 kV are commonly used in Switzerland or Germany. Furthermore, MV is also sometimes adopted for metro or tram lines, e.g., metro lines in China with 1.5 kV DC. Therefore, both ac-dc and dc-dc power converters are employed as the front-end for supplying the power. Furthermore, considering that trains use several types of power electronic applications, such as power drives, auxiliary converters, and ESS, a wide variety of power converters are required.

Amidst the e-mobility applications, aircraft seems to be far from all-electric implementation. This is sourced in the serious concern for the weight and volume of the system, which is currently highly limited because of heavy batteries, power electronics, as well as electric machines [15]. However, there are concepts for all-electric aircraft, and these use MVdc grids as a core with voltages as high as 10 kV [16, 17], requiring formidable support from dc-dc and dc-ac power converters. Nevertheless, either in current, jet engine-based, or future, all-electric aircraft applications, the use of MV power inverters for electric drives is a necessity.

Similarly, as in the aircraft applications, marine power electronics are also bound to MV voltage levels due to very high power ratings of megawatts and higher. Again, MVdc grids for energy distribution are considered, with voltage reaching 20 kV [18]. MV power inverters are also employed for variable frequency drives used in marine vessels [19]. All in all, even though the base characteristics and converter types are akin to the aircraft applications, because of the weight constraints, the end-product power electronics systems will vary vastly and require an individual approach.

Besides transportation uses, such as in the aforementioned aircraft and marine applications, MV motor drives are also vastly employed throughout the industry, with different power, torque, and speed requirements. To name a few, the mining, metal, oil, and gas industries can be distinguished, as well as water and chemical applications [20]. Therefore, there is a great emphasis on the MV power converters for electric drives.

Currently, over 1% of global energy is used in data centers [21]. This number is growing every year, especially with rapidly growing computational requirements, e.g., due to the employment of artificial-intelligence-driven applications throughout many aspects of our lives, starting from research, through industry, and up to personal use for entertainment. Even though at an end-level, these type of applications uses thousands of LV small-scale converters, the foundation of the system is a front-end grid converter, usually interfacing an MVac grid with voltages of around 10-20 kV, with an LVdc grid at the level of 400-800V [22]. Thus, MV SST ac-dc converters are of great interest.

The emerging technology concepts in the form of smart grids, fulfilling the roles of distribution and collector grids, interfacing RES and ESS, and many more, also favor MV levels due to increased flexibility compared to HV grids [23, 24]. Furthermore, constant progress in power electronics and semiconductor devices helps accentuate the advantages of MV over HV. An MVdc system can be employed as an interfacing grid between the HV transmission system and the many applications from its surroundings, e.g., RES, ESS, active compensation systems, as well as industry and residential loads [25]. The shift from an ac grid to a dc system leads to a more straightforward integration of generation and load systems, employing power converters without frequency synchronization and/or reactive power compensation. Furthermore, a lower number of conversion levels can also be achieved, leading

to increased efficiency. However, the installation cost of such a smart grid is high compared to a conventional approach.

As mentioned previously, MVdc grid applications have a wider variety of uses, for both on-shore, e.g., dedicated PV or wind DC grids, and off-shore applications, such as sub-sea power distribution systems. These types of smart grids require many power electronic converters for proper operation, grid converters from basic rectifiers to inverters; dc-dc converters, non-isolated and isolated, bi- and unidirectional; more sophisticated SST, and various protection and auxiliary systems.

Historically, DC grids were limited in voltage, which can be observed using the traction grid as an example, where the highest common voltages for AC and DC-type traction are 25 kV and 3 kV, respectively. The most visible bottleneck causing the limit in voltage for DC systems is the fact that natural zero crossing of the fault current in DC grids does not occur. This has drastically limited the interest in MVdc systems as conventional circuit breakers employed in ac systems are based on that phenomenon. However, with the advances in CB concepts, WBG semiconductor technology, fault detection in MVdc systems is becoming possible [26]. Therefore, as also mentioned before, MVdc grids are gaining more traction throughout many applications.

In order to sustain constantly increasing influence of distributed generation, as well as to counteract the negative influence of applications with noisy current draw, active compensation of harmonics of the grid currents is required [27]. In contrast to large-scale FACTS systems employed in HV transmission and distribution grids, lower-scale MV systems will have to be employed in MV grids. These applications support the grid, for example, by increasing the voltage quality through reactive power compensation or harmonic distortion minimization. These systems can take form in various ways, e.g., series, shunt, back-to-back, or multi-terminal configurations [28]. However, each system is still based on some kind of a power electronic system rated at MV.

Thus, as discussed, there is a plethora of MV power electronics applications for nearly every conversion type: isolated and non-isolated, bidirectional, and unidirectional; ac-ac, ac-dc, dc-ac, and dc-dc, with various and often distant requirements and characteristics. However, employing SiC-based power semiconductor devices instead of conventional Silicon counterparts may be deemed beneficial for each and one of them.

# 1.2 Silicon Carbide power devices advancing medium voltage power electronics

Inevitably, considering the vast application range of power electronics at medium voltage level, the requirements for the power converters, and specifically power semiconductor devices, can also vary intensively from application to application. However, the most common requirements for power switches employed in medium voltage converters can still be easily named and are depicted below:

- High breakdown voltage,

- Fast switching low switching energy

- Low conduction power losses,

- High-temperature capability,

- High reliability,

- Low cost.

Even though a specific set of preferred characteristics cannot be defined in general, one trait is vital for each application in the medium voltage range – high voltage blocking capability. Even with power semiconductor devices able to block several kilovolts, building two-level converters for the whole voltage range is impossible – converter topologies employing several power switches are needed. Thus, the higher the breakdown voltage, the lower the number of devices in a stack and the lower the system's complexity. Therefore, this characteristic is beneficial for all types of converters, from conventional topologies to advanced MMC systems.

Considering MOSFETs, the high current capability is not a precisely defined parameter of the device but rather is decided considering power loss and dissipation characteristics. Furthermore, parallel connection is generally seen as easy to implement in this case. Thus, to reach higher currents, simply the chip area of the power device is increased. Hence, the power losses are an important factor for the power devices. These are generally split into conduction losses associated with on-state voltage drop and switching losses depending on the turn-on and turn-off switching energy and the operating frequency. While minimizing power losses is an aim for most systems, the choice of a specific device varies depending on the application characteristics. For example, inherently soft-switching converters usually favor devices with minimized conduction losses, while the switching loss is not essential, as

these are vastly minimized anyway. Similarly, circuit breaker applications are not concerned about the switching loss since switching is not apparent during most of the operation.

Another trait strictly connected with the losses is the switching speed of a device. From one point of view, a higher switching speed results in a smaller overlap of voltage and current and leads to lowered power losses. Furthermore, shorter switching time allows for higher operating frequencies, which may lead to smaller passive components and enhanced system power density. On the other hand, higher switching speed may lead to issues with EMI, as the parasitic components become more crucial. Thus, this aspect also depends mainly on the type of application.

While the size of the chip is relatively small compared to other components of medium voltage power converters, it can still be important performance-wise, especially considering the aforementioned impact of parasitics. Moreover, the device's volume is often also directly connected with the power dissipation capabilities and the connections, which is especially vital for power modules that contain several chips within its structure, often employed in the medium voltage range. Overall, a small footprint and size of the device may be an important factor for certain applications.

Several medium voltage applications need to operate within harsh environments, e.g., in underground conditions, as in mining, or some automotive applications. In such cases, the temperature capability of the power devices can be a defining factor.

All the applications ideally should operate as reliably as possible. However, for some systems, it is more important than others. While a failure of part of a data center or one charger in a big EV station is not preferable, it does not lead to a crisis. On the other hand, a breakdown of an electric drive in a factory causes notable financial repercussions, while a malfunction of the electric system in an aircraft may even lead to catastrophic results with the cost of human lives.

Eventually, financial concerns are obviously an important aspect as well. Again, while in general, the lower the cost, the better, some applications may favor price over every other trait, while a different one would not consider price as a crucial factor.

All in all, each power device requirement can be considered more or less important for each system. Therefore, the choice of a specific power device for a defined application should be performed in accordance with its benefits and deficiencies. As an example, high-power applications favor the use of thyristors, as these are characterized by high voltage blocking levels and current capabilities. On the other hand, MOSFETs have relatively low voltage blocking proficiency, but they exhibit superior switching performance, while IGBTs are a middle ground between these two options. Finally, the introduction of the WBG power

# 1.2. SILICON CARBIDE POWER DEVICES ADVANCING MEDIUM VOLTAGE POWER ELECTRONICS

semiconductor technology, specifically SiC for medium voltage converters, allows for the construction of devices with higher blocking voltage capabilities and introduces the aforementioned MOSFETs into medium voltage range.

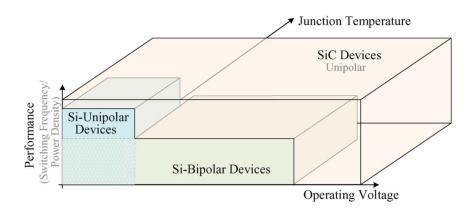

When most of the aforementioned requirements are concerned, the emerging silicon carbide technology seems to be a superior option compared to conventional silicon-based power devices - see Fig. 1.4. While Si technology has been well-established since the inception of power electronics in the 1960s, it simply cannot compete with SiC-based devices when medium voltage is considered, as the performance of the WBG counterparts is far ahead of the state-of-the-art Si power semiconductor devices in almost every aspect [29, 30], such as lower power losses, higher operating frequencies, and better temperature capabilities, while lagging behind primarily because of the relative immaturity of the technology – thus the cost is much higher, and the reliability is still a concern. However, as the technology improves, the drawbacks become less severe year-by-year [31], and thus SiC is the power device of choice for power electronics today, and even more so in the future [32, 33, 34, 31, 35] – see Fig. 1.4.

The story of power devices in Silicon Carbide technology begins in the 1990s when first analyses and concepts were shown [36], exhibiting the material's potential. However, it took many years from the concept level to actual device prototypes, and the first SiC devices were available on the market in the 2000s, namely SiC diodes and JFETs as the transistors [32]. However, because of the normally-on behavior of the JFETs, these have been quickly surpassed by MOSFETs, which have become the most popular SiC device to date, as they exhibit similar, exquisite performance but with normally-off operation. There have also been SiC BJTs presented; however, since voltage-controlled transistors are preferred, these have also quickly been pushed out by the MOSFET. Finally, the still-dominant technology in Silicon – the IGBT – has yet to be fully introduced onto the market with Silicon Carbide. While

Figure 1.4: The potential of Silicon Carbide technology over Silicon [29].

there have been prototypes reaching as high as 27 kV breakdown voltage [37], the manufacturing process is still far from commercialization, e.g., because of the intrinsic defects in the chips [38].

Focusing on the most popular type of power device, the SiC MOSFET, currently, there are commercially available transistors reaching as high as 3.3 kV [39], with prototypes at even 15 kV [40], that slowly begin to push out its Si-based counterparts. However, there is still room to improve as there are well-known, reliable, and proven Si devices in the form of Si IGBTs and Si thyristors. On the other hand, considering devices at 1.2 kV breakdown voltage and lower, SiC devices have already become the device of choice for LV power electronics and can be widely found not only in academia but also in industry applications [33].

That is due to the vast advantages of the SiC-based devices compared to their state-of-the-art Si adversaries, as has been proven by many works [29, 41, 30]. The many advantages include, amongst many, higher sustainable voltages, higher possible switching frequencies due to faster switching speeds and lower switching losses, minimized conduction losses as an effect of material properties, and higher tolerable junction temperatures. These provide the possibility to increase the converter performance, efficiency, as well as power density. The performance ratings are even more advantageous for the SiC over Si when MV is considered, as there are only bipolar devices available for the Silicon technology, and these are naturally less capable compared to unipolar devices.

The outstanding characteristics of SiC-based devices are inherently connected with the superior material properties of the WBG technology. More specifically, Silicon Carbide is distinguished by a larger (wider) band-gap, higher critical field, greater saturation velocity, and better thermal conductivity [36, 35].

The practical differences between power devices, both in Si and SiC technology, can be easily observed when comparing commercially available components rated at similar power level, both for discrete devices, as well as power modules. Table 1.1 depicts the parameters of two state-of-the-art 1.2 kV-rated discrete transistors in TO-247-4 packaging from the same manufacturer (on-semi) – FGH4L40T120LQD (Si IGBT) [42] and NTH4L040N120M3S (SiC MOSFET) [43]. As can be seen, considering the performance parameters, the SiC-based device is superior. The on-state losses are lower (16 vs. 25 W), the switching losses are almost ten times smaller, and the switching time is much shorter, with 72 ns compared with 339 ns of the Si IGBT. Furthermore, the gate charge is also much decreased, allowing for easier driving of the transistors. On the other hand, when the cost is considered, SI IGBT is cheaper. However, since 1200 V-class transistors in SiC are already well established on

# 1.2. SILICON CARBIDE POWER DEVICES ADVANCING MEDIUM VOLTAGE POWER ELECTRONICS

Table 1.1: Si IGBT and SiC MOSFET power device comparison for discrete transistors rated at 1.2 kV in TO-247-4 package, provided by the same manufacturer. [42, 43]

| Device type                                | Discrete transistor |                 |  |

|--------------------------------------------|---------------------|-----------------|--|

| Package                                    | TO-247-4            |                 |  |

| Manufacturer                               | on-semi             |                 |  |

| Device no.                                 | FGH4L40T120LQD      | NTH4L040N120M3S |  |

| Туре                                       | Si IGBT             | SiC MOSFET      |  |

| Breakdown voltage                          | 1200 V              |                 |  |

| On-state resistance (MOSFET) at 20 A       | -                   | $40 m\Omega$    |  |

| Saturation voltage (IGBT) at 20 A          | 1.25 V              | -               |  |

| Estimated on-state loss at 25 °C, 20 A     | 25 W                | 16 W            |  |

| Total switching time at 25 °C, 600 V, 20 A | 339 ns              | 72 ns           |  |

| Switching losses at 25 °C, 600 V, 20 A     | $1400~\mu J$        | 155 μJ          |  |

| Total gate charge                          | 227 nC              | 75 nC           |  |

| Current price [44, 45]                     | 8 \$                | 24 \$           |  |

the market, they are only three times more expensive for the considered case.

Furthermore, a comparison between power modules rated at 3.3 kV is depicted in Table 1.2. Again, when the performance of the device is considered, the SiC option is the obvious choice, with lower conduction losses (770 vs. 1013 W) and lower switching losses (0.63 vs. 1.36 J). However, the price disparity is even higher for power modules, as 3.3 kV SiC MOSFET power modules cost roghly ten times more than its 1.2 kV equivalents. All in all, considering both discrete devices and power modules, strictly focusing on performance, SiC devices are preferable over their Si counterparts and allow creating power converters with higher efficiencies and higher operating frequencies.

On the other hand, Silicon Carbide devices are still susceptible to certain drawbacks, mainly associated with the immaturity of the technology and its application in power electronics applications: in terms of manufacturing process of the chips and power devices [48, 49]; packaging of the devices, both in discrete and module setups [50, 51]; modeling, measurement and characterization [52, 53, 54]; as well as the design considerations for applying the SiC semiconductors into power converters to fully utilize their capabilities [55, 56].

While SiC technology has already been introduced many years ago, it is still not fully mature, especially compared to the Si devices, which have been investigated for over half a century. Thus, plenty of issues related to the manufacturing process of the SiC wafers remain. Several problems can be named: device reliability and device degradation are still

Table 1.2: Si IGBT and SiC MOSFET power device comparison for power modules rated at 3.3 kV, provided by the same manufacturer. [46, 47]

| Device type                              | Power module |               |  |

|------------------------------------------|--------------|---------------|--|

| Package                                  | kage nHPD2   |               |  |

| Manufacturer                             | Hitachi      |               |  |

| Device no.                               | MBM450FS33F  | MSM600GS33ALT |  |

| Туре                                     | Si IGBT      | SiC MOSFET    |  |

| Breakdown voltage                        | 3300 V       |               |  |

| On-state resistance (MOSFET) at 450 A    | -            | $3.8 m\Omega$ |  |

| Saturation voltage (IGBT) at 450 A       | 2.25 V       | -             |  |

| Estimated on-state loss at 25 °C, 450 A  | 1013 W       | 770 W         |  |

| Rise time at 25 °C, 1800 V, 450 A        | 120 ns       | 400 ns        |  |

| Fall time at 25 °C, 1800 V, 450 A        | 1300 ns      | 250 ns        |  |

| Switching losses at 25 °C, 1800 V, 450 A | 1.36 J       | 0.63 J        |  |

to be entirely determined in long-term operation [49, 57, 58], there are concerns regarding the gate oxide integrity [59, 60], near-interface traps [61], or threshold voltage instability [48]. Finally, the manufacturing process is imperfect; many production samples do not meet the specified parameters, for example, due to crystalline stacking faults, scratches, stains, or extra surface particles. Thus, the cost of SiC wafers is still very high [62]. Nevertheless, this is mostly a subject for material engineers working on power devices on a different level – thus, it is not further elaborated on within the thesis.

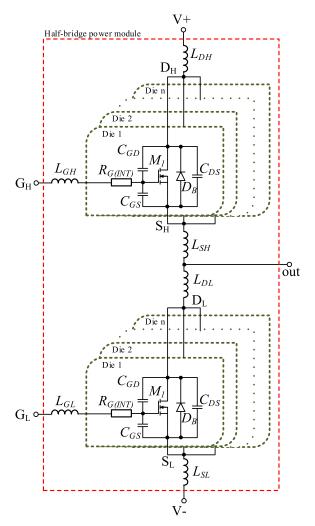

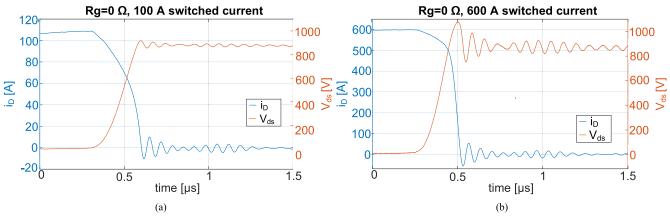

Packaging the power devices is also an important aspect of state-of-the-art SiC transistors, especially crucial for high-power MV power modules. Still, many current SiC devices directly adopt the packaging used for Si parts, e.g., to allow direct replacement of SiC instead of Si. However, since SiC power devices are characterized by different operating parameters, namely higher switching speeds, the parasitics of the devices and their packaging, including bonding, are the source of several issues [50, 51, 63, 64]. These include excess ringing, leading to increased EMI and additional power losses, limiting the possibilities of Silicon Carbide. This issue is specifically harmful when power modules are considered since these employ several chips paralleled to reach high sustainable currents and are usually bigger. Therefore, the path lengths, e.g., through bonding wires, are longer and induce more parasitics. Thus, there are works with improved power modules designed specifically for SiC, e.g., by employing busbar connections within the modules [65], and the subject is also considered in industry, as several companies, such as Microchip or Wolfspeed, offer SiC power modules with dedicated packaging. Still, since the packaging is also a concern for power

# 1.2. SILICON CARBIDE POWER DEVICES ADVANCING MEDIUM VOLTAGE POWER ELECTRONICS

device manufacturers, it is not studied further in the thesis.

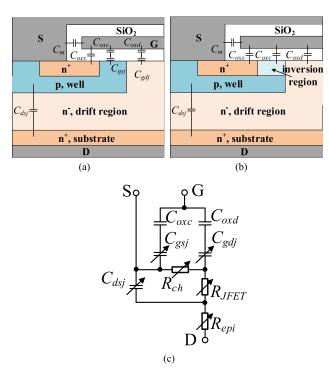

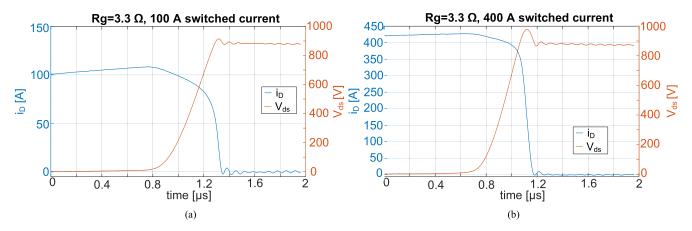

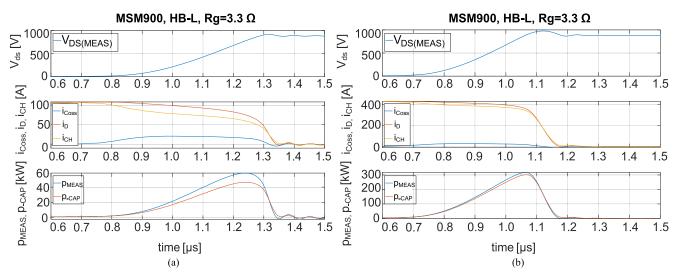

Considering the aforementioned traits of Silicon Carbide, as well as the structure of the chips themselves, there are plenty of concerns in regard to the proper modeling of the devices, their characterization, and methods to extract the design properties of SiC transistors to be employed in power electronics systems, namely, to precisely estimate power losses and temperatures. This is further associated with the complications regarding the measurements, for example, of the rapidly-changing currents [66].

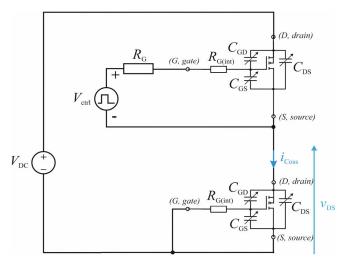

In order to investigate power electronic systems, as well as to design highly efficient and compact power converters, simulations are the tool of choice for many engineers and researchers. Thus, power device simulation models are developed. However, considering the high-speed switching behavior of SiC-based transistors, it is not a simple task [67]. Furthermore, the models developed for Si devices cannot be applied to SiC because of the different characteristics [68]. To emulate the switching process properly, the MOSFET capacitances must be considered and modeled [54, 69]. Still, the foundation of the models is the characterization based on the measurements of the actual devices, either done by the manufacturers and provided in the datasheets or performed further by the designers, e.g., via double-pulse tests. There are several methods presented, both for dynamic [53, 70, 71], and static [72] characterization of SiC MOSFETs. However, a simple methodology for characterizing the capacitance is still lacking, as the methods are either proposed only for low-voltage discrete devices, require supplementary active circuitry, or induce the need for precise calibration of the setup. Thus, this subject needs to be further investigated.

Following the modeling, another important aspect of the design of highly-performing MV power converters is the precise estimation of power losses. In general, three main methods for determining the converter power losses can be identified: electrical-based measurements, e.g., with a power analyzer; calorimetric approach, either with full chambers or via thermal flow measurement; as well as calculations [52, 73]. While the calorimetric approach provides the losses with the lowest error [74, 75], it is a complex approach that is more feasible for already-built converters. Considering the other method, the calculations heavily rely on the models and the experimental data, which, as mentioned, is not easily obtainable [76]. Finally, electrical-based measurements are generally less accurate compared to the calorimetric approach, e.g., because of the issues with probes [77]. However, these are usually very straightforward. Therefore, there are concepts for hybrid power loss estimation methods based on converging simple hardware experiments with calculations, which could be an invaluable tool for designing MV power converters. To this end, a novel concept for such a method is further exhibited in the thesis.

As was mentioned before, the exceptional switching speeds of SiC transistors raise a challenge for the design of power converters, from the gate drivers to the power circuit, in regard to diminishing the influence of the parasitics, so that the power losses [78] and generated EMI [79] are minimized [55, 56, 80]. One branch of research in this area is focused on the gate drivers; there are methods to employ active circuits that effectively lower the undesired effects [81, 82, 83]. However, these are often very complicated in practice, and the cost for medium voltage applications with tens of power devices is very high. The most obvious approach is the minimization of the parasitics within the power circuit [84, 85, 86]. However, this is not an easy task as the considerations for each converter will be different, depending on the topology, power circuit switching loops, and others. Thus, an important question regarding the design of MV power converters remains: What power switch concepts and topologies to choose in order to fully utilize SiC-based power devices in the medium voltage range?

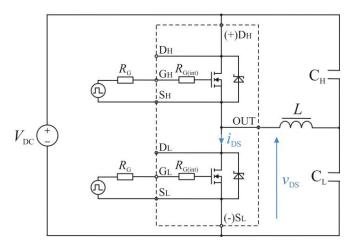

## 1.3 Power converter topologies in medium voltage

The most straightforward approach to constructing power converters is employing conventional two-level structures, often used in LV power electronics but also in a lower spectrum of MV applications [40, 87, 88, 89]. A worthy merit of this solution is its simplicity – a single power module can be used for the basic converter leg. Hence, the power circuit is minimized, limiting the influence of parasitics, and the cooling of the system can be less complex. On the other hand, properly driving SiC MOSFETs rated at tens of kilovolts is challenging, e.g., because of high dv/dt ratios [81, 90, 91]. Moreover, the cost of high-voltage SiC power modules is still immense.

Furthermore, when the MV range is taken into account, such an option is not a possibility for the higher voltages as the blocking voltage requirement exceeds the capabilities for off-the-shelf power transistors. As was already mentioned, there are SiC power devices reaching even 27 kV breakdown voltage. However, these are still being developed and are not widely available, and thus, the practical voltage limit for a single switch is much lower. Having a look at the power semiconductor device market, the breakdown voltage reaches about 10 kV for Si thyristors, 6.5 kV for Si IGBTs, and SiC MOSFETs are rated at maximally 3.3 kV. Therefore, when MV applications for voltages at 10 kV and higher, no power devices can single-handily block the required voltage. Thus, seeking other, more sophisticated power converter topologies is not only an option but a necessity for the MV range.

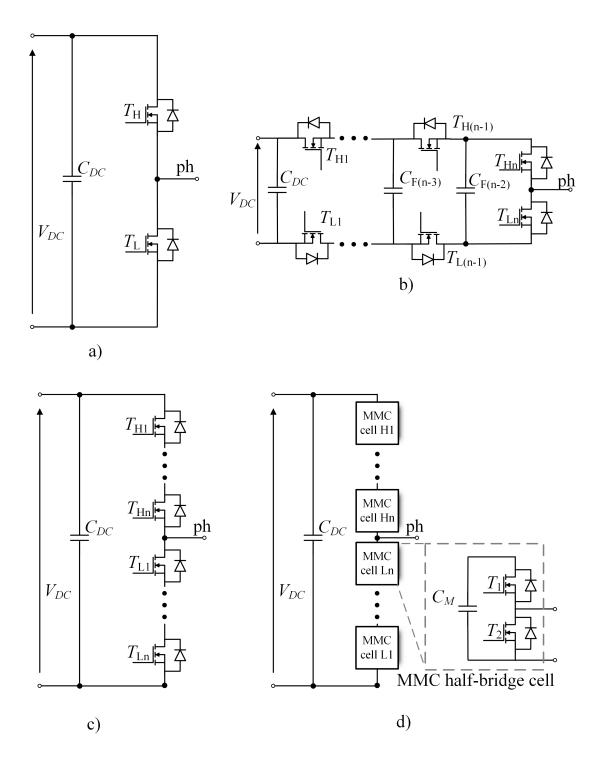

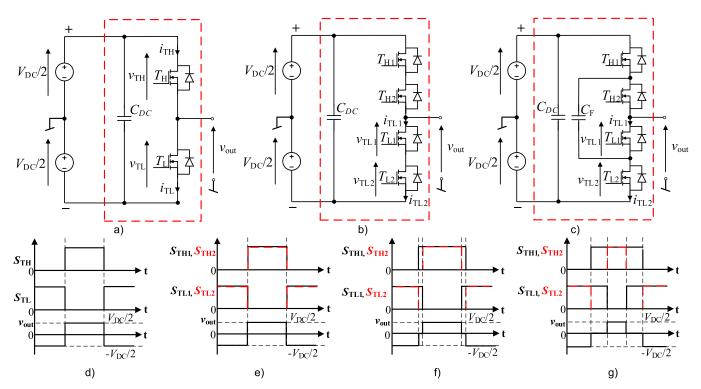

Hence, a number of methods to create power converters capable of sustaining higher volt-

age levels have been presented – see Fig. 1.5, where the most notable ones are considered, apart from the basic two-level topology (1.5b): conventional multilevel topologies (FCC shown here) 1.5b; series connection of power devices 1.5c; sophisticated MMC structures 1.5d; and quasi-two-level method – applicable for FCC and MMC topologies.

The first, most straightforward method for creating an MV power converter is the series connection (SC) of power transistors (Fig, 1.5c). Stacking single components in order to share the voltage stress across the elements is a well-established approach, easily incorporated for passive elements as well as non-controlled semiconductor devices, i.e., diodes. It can also be applied to active components, the power transistors. Except for the main advantage – limiting the voltage requirement of individual devices – a number of other benefits can be identified. In general, using a series connection leads to higher currents and efficiency per die area, as well as results in a lower cost of the system compared with basic two-level topologies [92].

Yet, the series connection of active power semiconductor devices, i.e., transistors, especially SiC MOSFETs, is not trivially applicable. Mainly because of the issues with the uneven voltage sharing between the transistors in the stack, both in static and dynamic states, appearing due to several factors: differences in gate driver and power circuit layout between the stacked devices [93, 92]; the influence of parasitic capacitances [94]; or the imperfection and parameter variations, e.g., capacitance characteristics, in the SiC MOSFET devices themselves [95, 94]. Therefore, circuits based on the series connection of SiC MOSFETs require the inclusion of voltage balancing methods, leading to additional complexity in power converters [96].

There are several voltage compensation methods dedicated to series-connected transistors, identified for both conventional, slow-switching Si devices [97], as well as newer works on the rapid SiC MOSFETs [96, 98]. In general, these can be divided into two groups – passive and active methods.

When the passive voltage compensation methods are considered, simplicity is vital. As the name suggests, there are no active components, and the voltage is usually balanced by the means of external circuits connected to the transistor. A standout example could be the snubber circuit, i.e., a capacitor and a resistor (sometimes also with a diode) connected in parallel to each stacked transistor [97, 95]. Effectively, the increased output capacitance of the transistors slows down each device and minimizes the effects of natural mismatches, leading to a more even voltage distribution. However, the voltage is usually never fully balanced. While the method itself does induce any extra loss on the power devices themselves, the snubber circuit does add a substantial amount of extra losses, thus limiting the system's

Figure 1.5: Generalized figure showcasing the possible methods to construct power converters in MV range: a) two-level topology with single power devices; b) classic multilevel topology (FC converter shown here); c) series connection of power transistors; d) MMC structure. Note that instead of a MOSFET, any power device can be applied as a switch for any of the topologies.

efficiency and adding components of considerable volume to the system. Nevertheless, the method is very simple and has proven to be a competent method for MV converters [99].

On the other hand, there are active voltage balancing methods based on closed-loop systems, minimizing the mismatches in the voltage based on the voltage measurements. While the general idea for the group is similar for each solution, the "actuator" deciding on the voltage distribution may differ. For example, in the active delay method [93], the voltage split is changed through minuscule delays added to specific transistors in the stack. Other approaches are based on extra current injection circuits [94] or other hardware-based techniques [100, 101]. Nevertheless, disregarding the type of active balancing, this group can be considered essentially lossless and can achieve near-equal voltage share. However, it comes with the cost of complicated circuitry and/or complex control, leading to an enlarged cost of the converters and possibly resulting in reliability issues in long-term operation.

In the end, the series connection of power transistors is a viable way to construct MV power converters. However, one must either accept simple snubber-based systems with additional power losses and lower power density or sophisticated, active circuits with no extra loss but with notably enlarged system complexity, e.g., through special control, additional measurements, or advanced gate drive circuits.

Another well-known solutions for creating MV power converters are the multilevel (ML) topologies. There is a vast array of different systems originating with cascaded topologies. Furthermore, considering only the most notable ones, neutral point clamped (NPC) [102] and its variations; the currently popular T-type converter [103, 104, 105]; the flying capacitor (FC) topology [106], depicted in Fig. 1.5b, and others [107] can be itemized. While there are several differences between the named topologies, a few general traits of conventional multilevel systems are distinguishable.

The main feature of multilevel converters is the concept of employing LV power devices to reach higher blocking voltages, similar to series connection systems. Although, here, the component structures are more advanced and employ other components in addition to the devices themselves, e.g., there are additional diodes in the NPC topology, or there are extra capacitors in the FC converters. Such complex circuits further necessitate the inclusion of more advanced modulation patterns when compared to two-level solutions.

In general, multilevel topologies are characterized by several advantages over two-level operated systems. The inclusion of more voltage levels in the output voltage provides the opportunity to improve the flexibility, achieve better recreation of sinusoidal currents, as well as bring lowered dv/dt ratio and EMI noise. Moreover, the power density can also be vastly improved, as the volume of the passive components, i.e., inductors, can be greatly

minimized [104]. On the other hand, the more voltage levels there are, the more complicated the structure and control become, as well as the system base cost increases – mainly because due to the need for voltage balancing. Nevertheless, multilevel systems are a popular choice for MV applications, especially in the lower voltage spectrum.

An important derivative of the multilevel converters is the MMC [108, 109, 110], introduced in 2001 and still widely investigated [111]. While it holds many similarities with the aforementioned, it is characterized by several attributes worthy of separate consideration. Most importantly, the main feature of the MMC is the modular aspect. Each leg of an MMC comprises many individual cells, usually identical ones. These cells can have different structures, e.g., as simple as the half-bridge cells depicted in Fig. 1.5d. Such a structure is especially beneficial for applications operating with notable voltages, where several or even tens of cells have to be employed, e.g., in HVdc systems [112, 113], but there are applications in the higher voltage spectrum of MV as well [108].

The inclusion of modularized, cell-based structures provides several vital aspects. First off, the reliability of MMC systems is high, as redundancy can be easily attained, and serviceability is improved as well [109]. Furthermore, the modular structure is beneficial in terms of system design, as the focus has to be put mainly on the cell, which is then multiplied. A similar approach is also seen for the control of the converter. Nevertheless, such a structure also is characterized by several drawbacks. For one, if a direct comparison with an FC system is considered, an MMC would exhibit at least twice the transistors assuming the same voltage level and also other components, i.e., capacitors. This also affects the size of the modules, which negatively impacts the switching loops, as well as the size of the whole system [114, 115]. All in all, regardless of the hindrances of MMCs, these are a common and noteworthy choice for elevated voltage applications in MV and HV ranges.

Finally, an emerging technique for the construction of MV power converters is the quasitwo-level (Q2L) approach. Originally, it was introduced as an alternative method of control for MMC systems that can drastically reduce the cell capacitance requirement at the cost of forgoing the multilevel aspect, as in a general scope, Q2L-controlled systems operate as conventional two-level systems [116, 117, 118, 119]. Furthermore, the method can also be effectively applied to FC converters [120, 121, 122]. The main difference in operation between Q2L and basic ML control methods is that in the former, the intermittent voltage levels are applied for a very brief time just to balance the voltages across the power devices, i.e., SiC MOSFETs, while in the latter, these are used for a notable amount of the switching period [123] – hence the difference is the energy stored in the capacitances.

Apart from the core difference resulting in intensively lowered volume of the capacitors,

as the stored energy can be reduced tenfold [119, 124], there are several other characteristics compared to conventional ML or MMC systems. The arm inductance requirement is immensely reduced, and the issue with circulating currents is nearly non-existent [125, 126]. Moreover, considering less severe capacitor voltage ripples, the closed-loop voltage balancing is also less challenging. On the other hand, the flexibility of shaping the output current is minimized; thus, higher inductance needs to be employed [119, 127].

Conventionally, the Q2L method was established with identical modulation patterns as in the conventional ML approach but with massively shortened intermittent levels. However, recently, there have also been presented concepts of employing the Q2L approach strictly to balance the voltages with the omission of the dv/dt ratio reduction, effectively deeming the alternate method equal to the approach with series-connected transistors [128, 129]. Thus, such implementation of Q2L control can be seen as a simpler alternative for more complex active voltage balancing methods, further considered in the publications included in the thesis. All in all, the Q2L method, in either form, is a notable method for MV power converters, recently gaining a lot of interest in academia and industry.

The general characteristics of the discussed approaches are summarized in Table 1.3. When the complexity is considered, the single device is definitely the most straightforward option, both in terms of control and system design, while MMC is characterized by a sophisticated structure and convoluted control. Since the cost of high-voltage-breakdown power devices is still quite enormous, solutions that employ several LV transistors are the most favorable here. Volume-wise, the single-device option can be, again, considered the best one. On the other hand, series-connection-based circuits with snubbers require notable volume, similar to the MMC systems. The situation is akin to the parasitics and the layout complexity. Because of the redundancy option, MMCs are favored in terms of reliability, while the lowest power losses can be achieved with the solutions employing simple structures with LV power devices – the actively balanced SC and Q2L systems. Finally, apart from the single device, two-level option, any method can theoretically reach any blocking voltage, but ML-MMC and Q2L-MMC would be the choice for notable voltage levels.

Considering all the mentioned methods and their characteristics, the approach for creating converter legs for MV applications is not a trivial endeavor. Depending on the end application, various traits may be seen as critical, and thus, a single, best option cannot be named in general. Furthermore, the situation becomes even more complicated as full converter topologies come into play, whether the system has to be ac-dc or dc-dc, have the insulation or not, if the structure has to be combined with other structures to ensure other features, e.g., soft-switching; and many more.

| Parameter        | Single device | SC - passive | SC - active | Q2L    | ML     | MMC    |

|------------------|---------------|--------------|-------------|--------|--------|--------|

| Complexity       | low           | medium       | high        | medium | medium | high   |

| Cost             | high          | medium       | medium      | medium | high   | high   |

| Volume           | low           | high         | medium      | medium | medium | high   |

| Parasitics       | low           | medium       | medium      | medium | medium | high   |

| Reliability      | medium        | medium       | low         | low    | medium | high   |

| Efficiency       | medium        | low          | high        | high   | high   | medium |

| Blocking voltage | low           | high         | high        | high   | high   | high   |

Table 1.3: Characterization of different methods for MV power conversion.

#### 1.4 Motivation & aim

The main motivation behind the thesis is the constant advances in SiC-based power device technology that allow for more straightforward construction of high-performance medium voltage power electronics. Medium voltage power electronics have been widely analyzed and constructed for many years already, especially for high power systems, mainly since an increase in the voltage leads to lower current, which reduces the conduction power losses and further enables the lower volume of the connections, e.g., busbars and cables. However, until recently, medium voltage applications were bound only to Silicon devices, such as IGBTs, or IGCTs, since only these types of power devices could operate with breakdwon voltages higher than 1 kV. It is well known that these devices are characterized by many drawbacks, e.g., the tail current of IGBT, leading to relatively high power losses, the nonfull controllability of the thyristors, or the high cost of IGCTs. Then, the introduction of SiC power devices brought the highly performing MOSFET into the MV range, with prototype devices at 10 kV breakdown voltages and higher. However, although SiC-based devices already allow for a substantial enhancement of MV converters over their Si-based counterparts, several issues constraining the appropriate utilization of Silicon Carbide still need to be addressed. The most important ones include: how to properly construct the hardware that allows for fast-switching operation, how to model the converters employing SiC-based semiconductor devices and accurately estimate the power losses, what topologies and control methods are the most efficient.

Thus, the aim of the dissertation was to study the possibilities of effective electric energy conversion in medium voltage range with power converters based on Silicon Carbide power devices.

Other, more specific goals can be established as parts of the core aim and are depicted

below.

- Methods to precisely characterize the output capacitance of MV SiC MOSFETs power devices allowing for accurate estimation of power losses based on simple experimental systems can be established.

- Methods to accurately estimate MV SiC device power losses within power converters based on simple experimental setups can be established.

- There are several converter topologies that can effectively utilize SiC power devices in medium voltage power electronic systems.

- Quasi-two-level method is a prominent method for creating SiC-based MV power converters.

- TCM-Q2L control technique allows the construction of high-efficient dc-dc SiC-based MV power converters operating at high frequency.

- Quasi-square-wave technique can be employed to achieve fully soft-switched operation of SiC power MOSFETs in MV range.

### 1.5 Publications included in the dissertation

The dissertation contains the following five publications, where the author is a co-creator:

- [P1] J. Rąbkowski, M. Zdanowski, **R. Kopacz**, F. Gonzalez-Hernando, I. Villar and U. Larrañaga, "From the Measurement of COSS–VDS Characteristic to the Estimation of the Channel Current in Medium Voltage SiC MOSFET Power Modules," in IEEE Transactions on Instrumentation and Measurement, vol. 72, pp. 1-10, 2023, Points according to the Ministry of Education and Science: **100**, Impact Factor: **5.332**. Contribution of the dissertation author: **25**%. [130]

- [P2] J. Rąbkowski, H. Skoneczny, R. Kopacz, P. Trochimiuk, G. Wrona, "A Simple Method to Validate Power Loss in Medium Voltage SiC MOSFETs and Schottky Diodes Operating in a Three-Phase Inverter", Energies, 13, 4773, 2020. Points according to the Ministry of Education and Science: 140, Impact Factor: 3.252. Contribution of the dissertation author: 25%. [131]

- [P3] P. Trochimiuk, R. Kopacz, K. Frąc and J. Rąbkowski, "Medium Voltage Power Switch in Silicon Carbide—A Comparative Study," in IEEE Access, vol. 10, pp. 26849-26858, 2022. Points according to the Ministry of Education and Science: 100, Impact Factor: 3.476. Contribution of the dissertation author: 40%. [132]

- [P4] **R. Kopacz**, M. Harasimczuk, P. Trochimiuk, G. Wrona and J. Rąbkowski, "Medium Voltage Flying Capacitor DC–DC Converter With High-Frequency TCM-Q2L Control," in IEEE Transactions on Power Electronics, vol. 37, no. 4, pp. 4233-4248, April 2022. Points according to the Ministry of Education and Science: **200**, Impact Factor: **5.967**. Contribution of the dissertation author: **40**%. [129]

- [P5] **R. Kopacz**, M. Harasimczuk, P. Trochimiuk and J. Rąbkowski, "Investigation of Soft-Switching QSW Technique in DC/DC SiC-Based Flying Capacitor Converter With Q2L Control," in IEEE Transactions on Industrial Electronics, vol. 70, no. 9, pp. 9035-9045, Sept. 2023. Points according to the Ministry of Education and Science: **200**, Impact Factor: **8.162**. Contribution of the dissertation author: **50**%. [133]

The summarized bibliometric parameters for the core publications [P1]-[P5] are depicted in Table 1.4.

Table 1.4: Summary of the parameters of the core publications included in the dissertation.

| Summarized for [P1]-[P5]                                  |               |  |  |

|-----------------------------------------------------------|---------------|--|--|

| Points according to the Ministry of Education and Science | Impact Factor |  |  |

| 740                                                       | 26.189        |  |  |

### 1.6 Other achievements

Besides the mentioned publications, core for the dissertation, the author has also contributed to several other publications (5 journal papers, 9 conference proceedings), closely related to the subject of the thesis.

Journal publications:

[J1] J. Rąbkowski, **R. Kopacz**, "Extended T-type inverter", in Power Electronics and Drives, vol.3, no.1, 3918, pp.55-64. Points according to the Ministry of Education and Science: **20**, Impact Factor: **N/A**. Contribution of the dissertation author: **30**%. [134]

- [J2] B. Lasek P. Trochimiuk, R. Kopacz, and J. Rąbkowski, "Parasitic-based active gate driver improving the turn-on process of 1.7 kV SiC power MOSFET", in Applied Sciences, 2021, 11, 2210. Points according to the Ministry of Education and Science: 100, Impact Factor: 2.7. Contribution of the dissertation author: 15%. [135]

- [J3] P. Trochimiuk, R. Kopacz, G. Wrona and J. Rąbkowski, "Active Voltage Balancing of Series-Connected 1.7 kV/325 A SiC MOSFETs Enabling Continuous Operation at Medium Voltage," in IEEE Access, vol. 9, pp. 8604-8614, 2021. Points according to the Ministry of Education and Science: 100, Impact Factor: 3.476. Contribution of the dissertation author: 30%. [93]

- [J4] R. Kopacz; M. Harasimczuk, B. Lasek, R. Miśkiewicz, and J. Rąbkowski, "All-SiC ANPC Submodule for an Advanced 1.5 kV EV Charging System under Various Modulation Methods", Energies 2021, 14, 5580. Points according to the Ministry of Education and Science: 140, Impact Factor: 3.252. Contribution of the dissertation author: 40%. [136]

- [J5] R. Kopacz, M. Harasimczuk, J. Rabkowski, R. Sobieski, "Three-Level Interleaved Non-isolated DC/DC Converter as a Battery Interface in an EV Charging System with Bipolar DC-Link", Przegląd Elektrotechinczny, vol. 5, 2023. Points according to the Ministry of Education and Science: 70, Impact Factor: N/A. Contribution of the dissertation author: 55%. [107]

#### Conference proceedings:

- [C1] **R. Kopacz**, D. Peftitsis and J. Rabkowski, "Experimental study on fast-switching series-connected SiC MOSFETs," European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), Warsaw, Poland, 2017, pp. P.1-P.10. Contribution of the dissertation author: **50%**. [95]

- [C2] J. Rabkowski, S. Piasecki, and R. Kopacz, "An extended T-type (eT) inverter based on SiC power devices", European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), Riga, Latvia, 2018, pp. P.1-P.10. Contribution of the dissertation author: 20%. [134]

- [C3] P. Trochimiuk, R. Kopacz, G. Wrona and J. Rąbkowski, "Medium voltage power switch based on 1.7 kV SiC MOSFETs connected in series inside power modules," European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), Genova, Italy, 2019, pp. P.1-P.10. Contribution of the dissertation author: 25%. [98]

- [C4] R. Kopacz, P. Trochimiuk, G. Wrona and J. Rąbkowski, "High-frequency SiC-based medium voltage quasi-2-level flying capacitor DC/DC converter with zero voltage switching", European Conference on Power Electronics and Applications (EPE '20 ECCE Europe), Lyon, France, 2020, pp. P.1-P.10. Contribution of the dissertation author: 50%. [122]

- [C5] J. Rabkowski, D. Peftitsis, R. Sobieski, M. Harasimczuk, R. Miśkiewicz, K. N. Kumar, R. Kopacz, K. Kalinowski, and P. Trochimiuk, "Advanced charging system with bipolar DC-link and energy storage",2022 Progress in Applied Electrical Engineering (PAEE), Koscielisko, Poland, 2022, pp. 1-6. Contribution of the dissertation author: 10%. [137]

- [C6] M. Harasimczuk, K. Kalinowski, R. Miskiewicz, R. Kopacz, B. Lasek and J. Rabkowski, "Three-Level ANPC Converter as an Input Stage of an EV Charging System with Bipolar DC Link," PCIM Europe 2022; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 2022, pp. 1-6. Contribution of the dissertation author: 10%. [138]

- [C7] J. Rąbkowski, R. Kopacz, R. Sobieski, M. Zdanowski, P. Trochimiuk and S. Piasecki, "Continuous operation of medium voltage SiC power modules in the test circuit," 2022 Progress in Applied Electrical Engineering (PAEE), Koscielisko, Poland, 2022, pp. 1-6. Contribution of the dissertation author: 30%. [139]

- [C8] R. Sobieski, R. Miskiewicz, J. Rabkowski and **R. Kopacz**, "Two-phase interleaved DC-DC converter with 3.3 kV SiC MOSFET modules," 2023 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (ESARS-ITEC), Venice, Italy, 2023, pp. 1-5. Contribution of the dissertation author: **10%**. [89]

- [C9] R. Kopacz, M. Harasimczuk J. Rabkowski and R. Sobieski, "Experimental evaluation of inductor configurations and modulation techniques in an interleaved three-level DC/DC SiC-based converter," 2023 IEEE 17th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Talinn, Estonia, 2023, pp. 1-6. Contribution of the dissertation author: 50%. [140]

#### Awards:

• Scholarship of The Ministry of Education and Science for students with exceptional scientific contribution, 2019.

#### 1.6. OTHER ACHIEVEMENTS

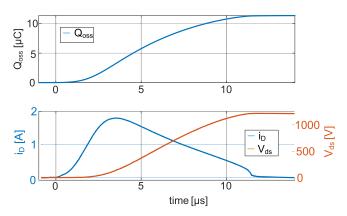

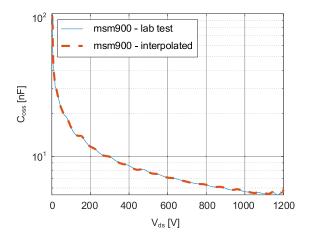

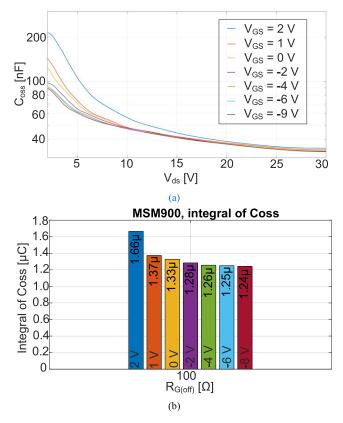

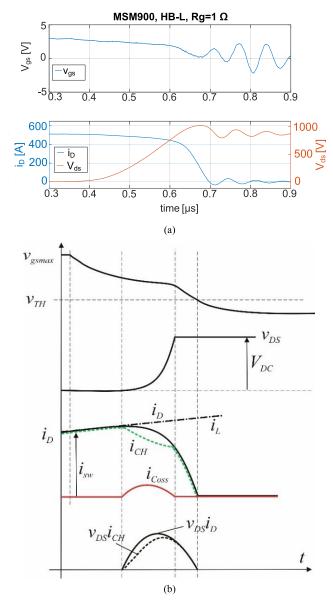

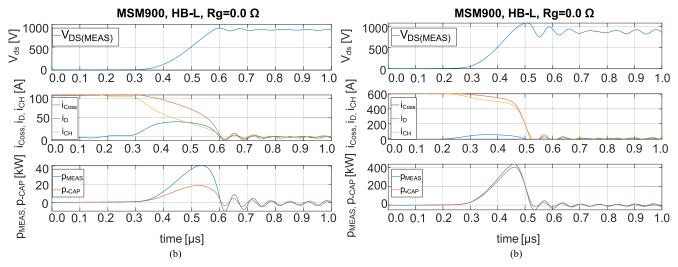

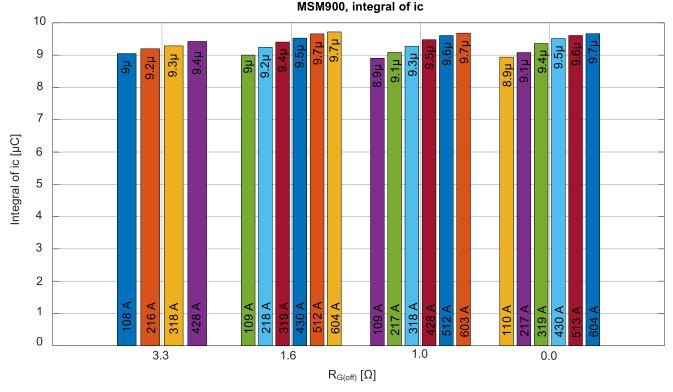

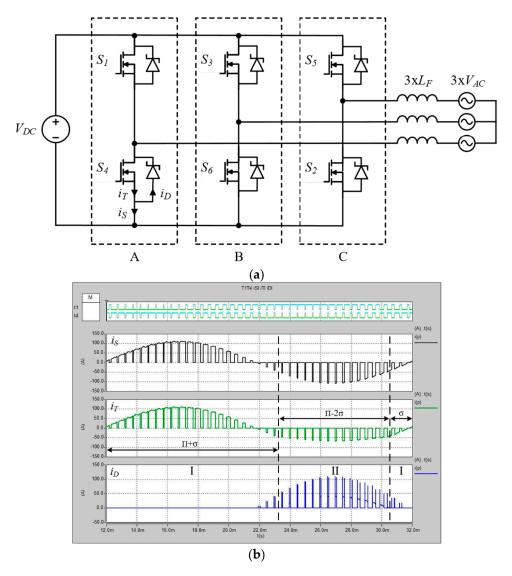

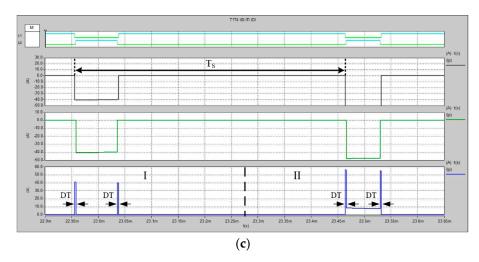

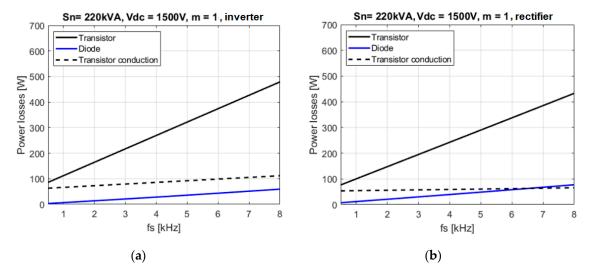

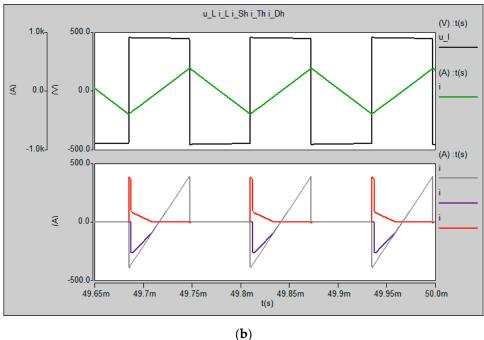

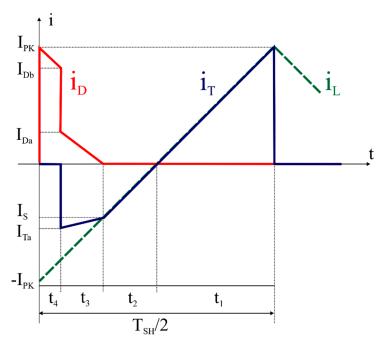

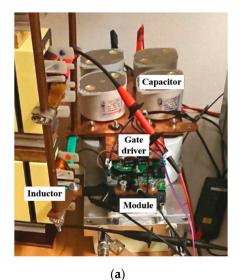

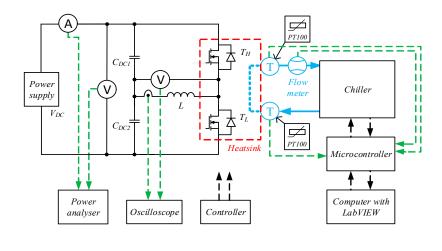

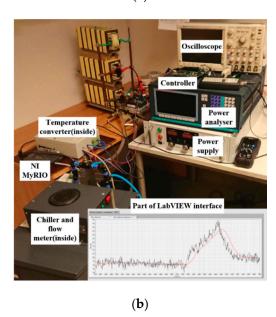

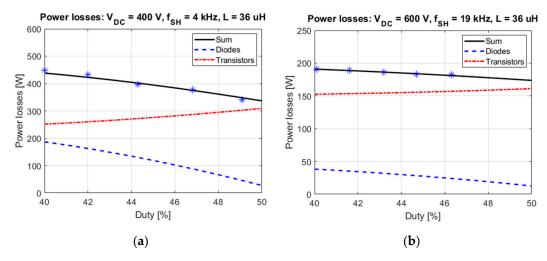

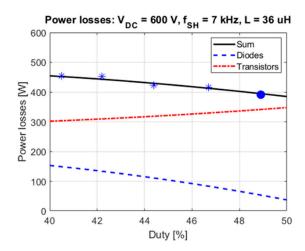

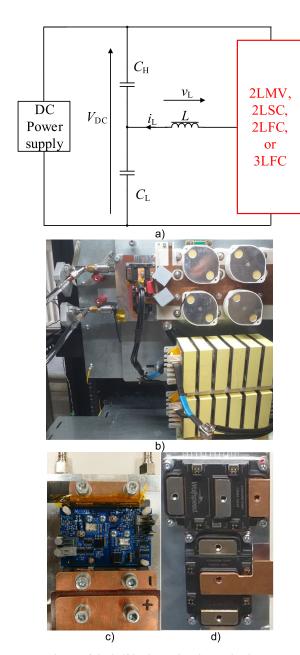

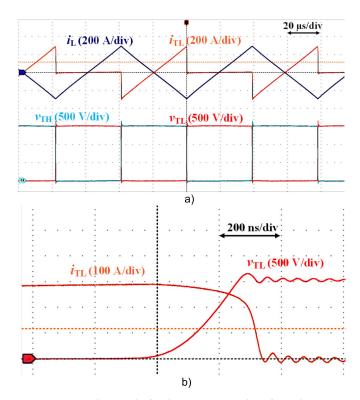

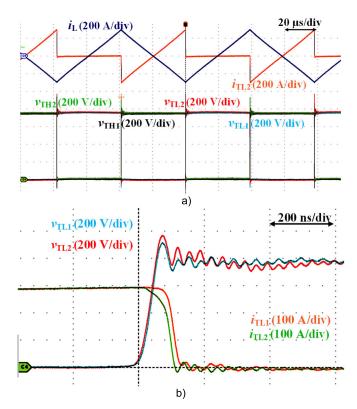

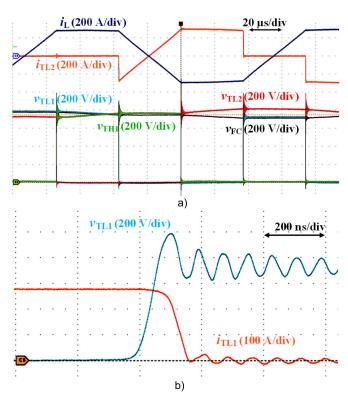

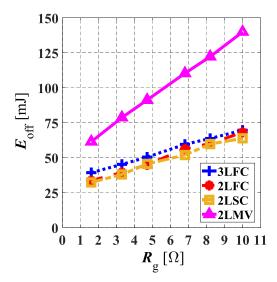

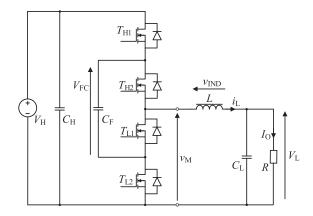

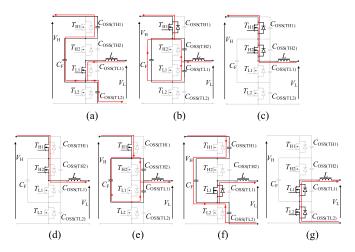

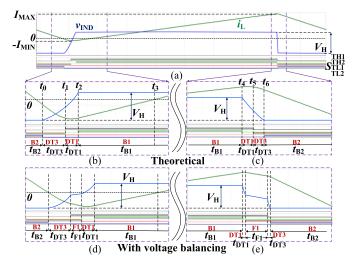

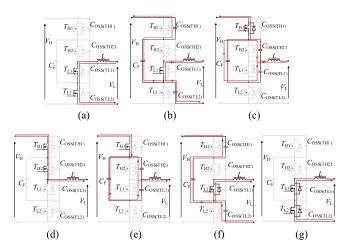

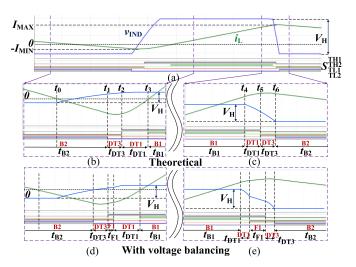

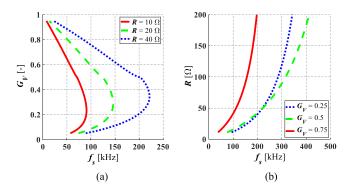

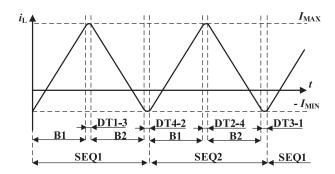

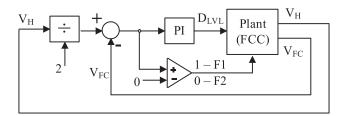

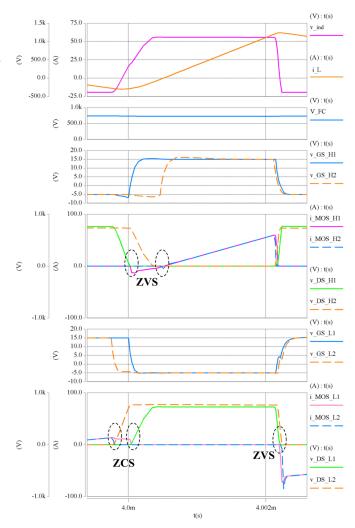

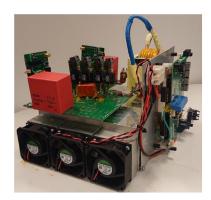

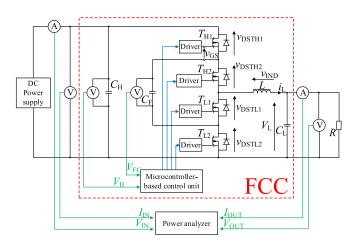

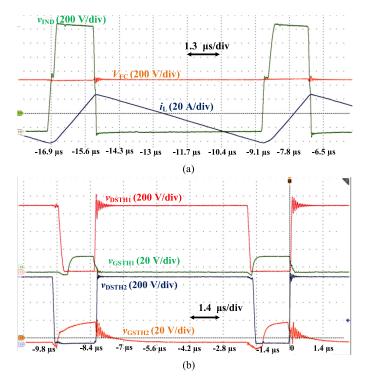

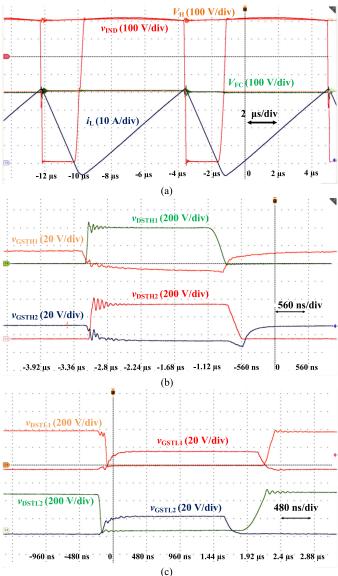

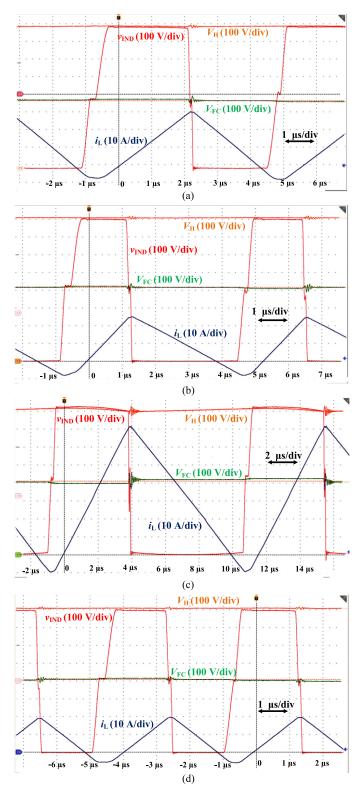

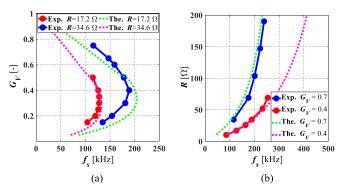

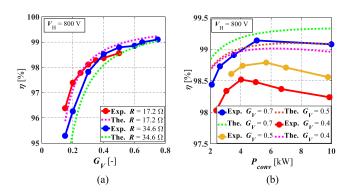

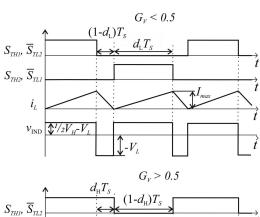

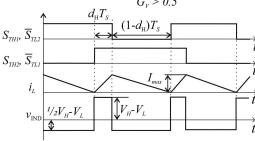

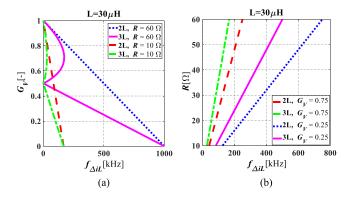

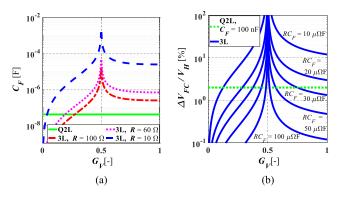

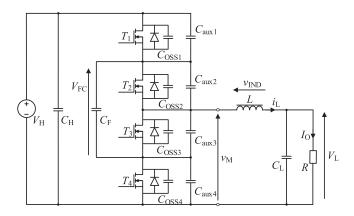

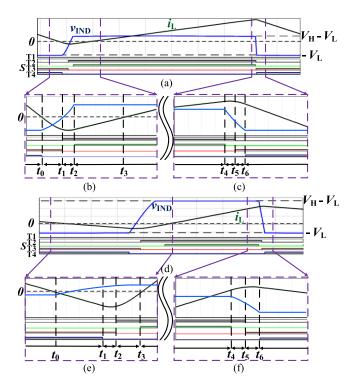

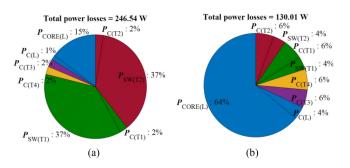

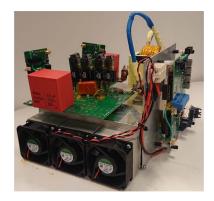

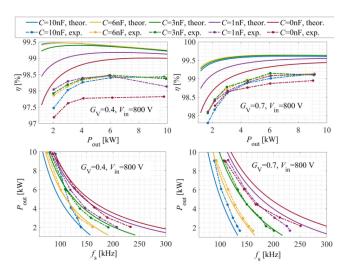

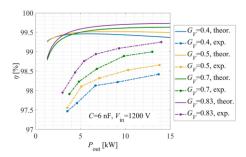

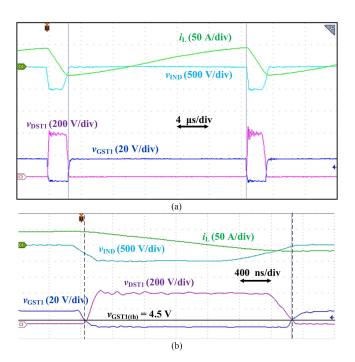

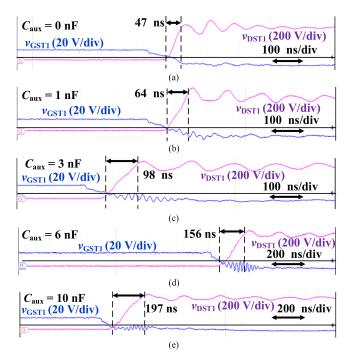

- Scholarship of The Ministry of Education and Science for young scientists with exceptional scientific contribution, 2023.